지난 과정에 이어서 CMOS공정과 금속 layer까지 쌓는 것으로 마무리한다.

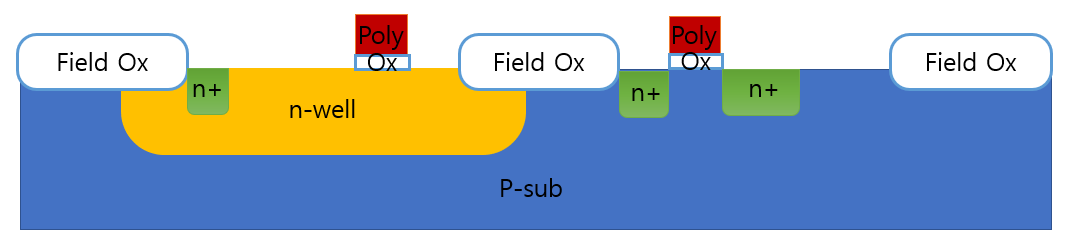

23.Photolithography : #4 n+ S/D mask 사용

24. n+ S/D implantation : As 사용

: MOS소자의 RC delay를 발생시키는 기생 capacitor는 gate와 n+영역의 overlab때문에 생긴다. 따라서 RC delay를 줄이기 위해서는 gate와(아래 단면도의 경우 poly -si) n+도핑되는 영역이 lateral하면 안되고 도핑 profile이 anisotropic해야한것이 좋다. 24번 공정이전에 poly si로 gate를 먼저 만들어 둔뒤에 implantation을 진행하면 poly si gate가 mask가 되어 정확한 경계에 맞춰서 도핑이 가능하다. 이러한 공정을 self-aligned 이라고 한다.

25. PR strip (Ashing)

26. n+ S/D Annealing (Thermal)

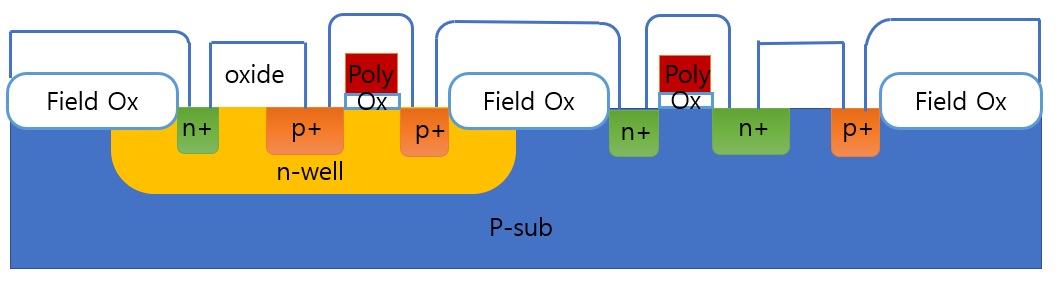

27. 23~26번 과정을 B으로 바꿔 동일하게 진행한다. : p+ 영역 implatation

28.Oxide deposition(CVD)

: Oxidation에 비해서 CVD는 낮은 온도에서 진행된다. 또한 산소 기체를 이용하여 실리콘 표면에 oxide를 growth시켜 실리콘 내부와 외부로 oxidation되는 것과 달리 CVD로 deposited oxide를 만들면 산소와 실리콘 기체를 둘다 사용하고 substrate의 종류에 상관없이 만들 수 있다. Growth는 CVD에 비해 느리지만 품질이 좋아 trap(defect)이 적고 breakdown Voltage가 높다. CVD는 1시간 정도면 수㎛를 쌓을 수있어서 (oxidation은 3시간에 2 ㎛ 정도) 두꺼운 보호막이나 절연막이 필요할 때 주로 사용된다.

28.Photolithography : #5 contact mask 사용

29.Oxide Dry etching

30.PR strip

31. Metal deposition

추가 예정

'반도체 > 공정' 카테고리의 다른 글

| [GeOI substrates] flipped Smart-Cut 공정 (2) | 2022.04.03 |

|---|---|

| [정리] n-well CMOS 공정 flow (상) (1) | 2022.03.31 |