반도체 소자 카테고리에서 다룬 GOI구조를 만들기 위해서는 smart cut 공정이 필요하다. 기존의 smart cut은 SOI 구조용 wafer를 제조하는 공정법이다. smart cut 공정은 2가지 wafer ( handle wafer , device wafer)를 결합하는데 결합되는 wafer중 하나에 수소 이온을 주입하여 수소 이온주입층을 형성한 후 열처리에 의해 이 수소 이온 주입층을 중심으로 wafer를 분리시키는 공정이다. 구체적인 방법은 다음과 같다.

< Smart-Cut SOI wafer fabrication >

1. 디바이스 웨이퍼에 열산화공정으로 표면에 절연막(SiO2)를 형성한다. 이 절연막은 SOI웨이퍼에서 BOX(Buried Oxide Layer: 매몰 산화층)역할을 한다. 필요에 따라 수십~수천Å 두께로 형성할 수 있다.

2. 디바이스 웨이퍼에 고전압의 수소 이온을 주입한다. 특정 에너지를 갖는 수소 이온을 이용하여 실리콘 산화막 아래의 디바이스 웨이퍼의 표면으로부터 원하는 깊이에 수소 이온 주입층을 형성시킨다.

3. 디바이스 웨이퍼와 핸들 웨이퍼를 세정하여 표면 오염물을 제거한 후 두 웨이퍼를 위아래로 결합시킨다.

접착 방법은 핸들 웨이퍼를 수평으로 뉘어 놓은 채 그 위로 디바이스 웨이퍼의 BOX 부분을 평행하게 위치시킨 후 상온에서 전체 웨이퍼의 표면이 동시에 접촉되록 접착시킨다.

*이때 두 웨이퍼는 친수성(hydrophilic) 조건하에 수소 결합에 의해 상호 접합된다.

4. 저온과 고온의 2단계 열처리를 하여 수소 이온 주입층을 분리한다.

1 단계 : 질소 분위기와 약 200℃ 정도 온도에서 약 2시간 - 디바이스·핸들 웨이퍼의 접합 에너지 증대.

2 단계 : 500℃에서 약 1~2시간 - 수소 이온 주입층의 분리 유도

5. 실리콘 층의 분리면에서 CMP를 원하는 소자의 channel 두께까지 진행한다.

이 제조 공정에서 수소 이온 주입층 분리가 일어나기 위해서는 핸들 웨이퍼와 디바이스 웨이퍼를 접합시킬 때, 이 두 웨이퍼 사이에 강한 접합 강도가 요구된다. 충분히 강하게 접합되지 않으면 접합된 계면에서 먼저 분리가 일어나 접합이 떨어질 수 있다. 따라서 접합 강도를 높이기 위한 열처리 공정이 필수적인데 처음부터 고온의 열처리를 하는 것 또한 수소 이온의 out diffusion 되므로 수소 이온층 분리가 완벽하게 일어날 수 없다. 또한 두 웨이퍼가 다른 열팽창 계수를 가지면 고온에서 웨이퍼의 변형,비접합, 파괴등이 발생 될 수 있다. 이러한 2단계 열처리 과정은 시간도 오래걸리고 공정 단계도 복잡하게 되어 생산성이 떨어지는 문제가 있다. 이를 해결 하기 위해 디바이스 웨이퍼의 접합표면을 플라즈마 활성화 처리(상온에서 질소가스 사용)하여 웨이퍼 표면의 원자 간에 결합 밀도와 화학 반응성을 증가시킨다. 이로인해 접합 강도가 높아지게 된다. 또한 열처리 과정을 400℃ 이하의 온도에서 진행하여 접합 강도 강화와 분리가 같은 온도에서 일어나도록 공정을 단순화하고 시간을 단축 할 수 있다. 또한 저온의 열처리 과정은 고온에 비해 수소 이온의 out diffusion이 줄어들어 표면의 거칠기도 줄어든다. 표면의 거칠기는 thin channel 소자일수록 전자의 mobility에 큰 영향을 주는 요소 이다. 표면이 거칠수록 interfacer trap에 의해 캐리어의 mobility가 떨어 질 수 있다.

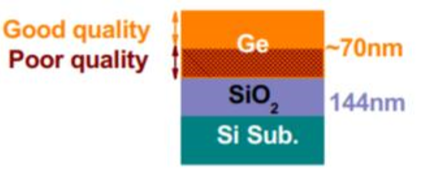

위의 전통적인 SOI구조에서 핸들웨이퍼 부분,즉 channel부분을 Germanium으로 바꾼 것이 GOI 구조이다. 이는 소자 미세화로 인해 channel의 두께와 길이가 줄어들게 되면서 발생하는 여러 문제등으로 누설전류가 증가하고 캐리어의 이동도가 떨어지는 문제를 해결하기위해 캐리어 이동도가 Si보다 높은 Ge를 사용한 것이다. 이러한 ultrathin- body (UTB) GOI구조는 SOI구조 보다는 short channel effect(SCE)에 면역이 있긴 하지만 채널 두께가 20nm이하가 되면 캐리어의 이동도가 감소한다. 이 이동도의 감소는 Smart-Cut 공정으로 인해 Ge/BOX interface 또는 Ge/SiO2 interface에서 crystalline(결정성) 품질이 떨어지기 때문이다. 따라서 flipped GOI 제조공정이 제안된다.

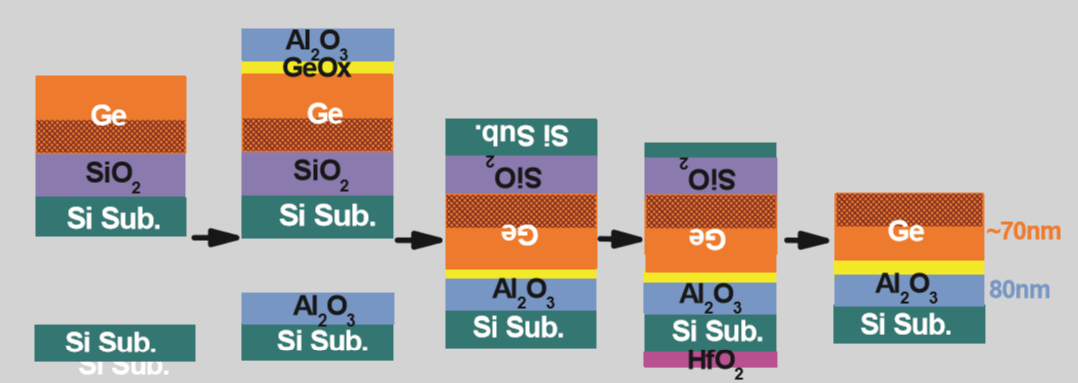

< flipped GeOI fabrication >

1. Smart-Cut GeOI donor wafer에 40nm 두께의 Al2O3를 ALD(atomic layer deposition)로 증착한다. (BOX 두께 증가)

2. 좋은 계면특성을 위해 ECR(electron cyclotron resonance) PPO(plasma post oxidation)으로 GeOx/Ge interface를 형성한다.

3. handling Si wafer에도 ALD 로 40nm의 Al2O3를 증착한뒤 donor wafer와 결합시킨다. 이는 진공상태의 300℃ 에서 1시간 동안 annealing을 진행한다.

* 이 과정에서 Si handle wafer를 heavily-doped하면 back gate control이 가능하다.

4. mechanical polishing ( with diamond slurry)를 이용해 donor wafer의 silicon substrate를 100㎛ 이하로 얇게 깎는다.

5. selective wet etching를 하기 전에 handling wafer 뒷표면에 ALD로 HfO2를 증착하여 보호한다. 이는 hard mask이다.

6. SiO2를 TMAH(teramethylammonium hydroxide) 150℃ 로 etch한다.

그러나 이 공정법에서도 10nm이하로 채널 두께가 얇아지면 거친 표면으로 두께 변동성 문제가 제기된다. 따라서 참고 논문에 따르면 reactive ion etching (RIE)와 열산화 ( thermal oxidation )의 2가지 thining process를 조합하여 solution을 제시한다. RIE를 추가적으로 진행하면 original GeOI와 비교적해보더라도 준수한 표면 거침도를 가진다.

*참고 논문 : Characterization of ultrathin-body Germanium-on-insulator structures and MOSFETs on flipped Smart-Cut GeOI substrates .

*참고 발명 : Methods of manufacturing semiconductor devices that include performing hydrogen plasma treatment on insulating layer

'반도체 > 공정' 카테고리의 다른 글

| [정리] n-well CMOS 공정 flow (하) (0) | 2022.04.01 |

|---|---|

| [정리] n-well CMOS 공정 flow (상) (1) | 2022.03.31 |